Публикую выдержки из переписки со своей рабочей группы для изучения русского профессионального языка разработчиков железа. И для обучения всех заинтересовавшихся конструктивным диалогом.

Все необходимые файлы, упомянутые в переписке, могу выложить на гитхабе:

На мой взгляд компьютерный эксперимент быстрей и удобней, чем натурный. В нашем случае - моделировать на Spice легче, чем возиться с осциллогорафом. Однако моделирование на Spice адекватно только в том случае если Spice модель (уравнения + коэффициенты) точно описывает настоящие транзисторы и соединения.

Поэтому мне хочется разместить в майском запуске тестовые структуры,

которые можно будет потом обмерять. По результам измерений можно будет потом провести характеризацию - подогнать коэффициенты для какой-нибудь транзисторной модели с OperSource уравнениями - BSIM3, HSIM. Научившись получать коэффициенты непосредственно из результатов измерения, мы не будем зависеть от коммерческих симуляторов с закрытыми моделями - HSpice, Spectre, Avosim .

За образец можно взять тестовые структуры, которые использует Mosis для

характеризации:

http://www.mosis.org/Technical/process-monitor.html

Ксожалению их может быть недосаточнодля обмера емкостей транзистора.

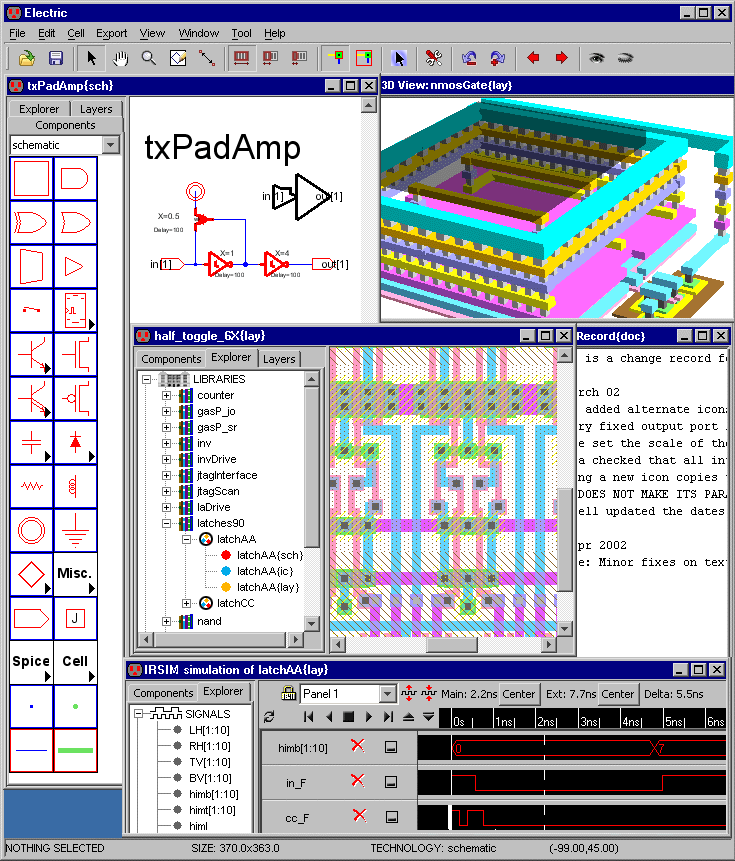

Библиотечные элементы собранны без DRC ошибок, схема счетчика проверялся в Altere Ч., а вот в Electric

схем не работает.

IRSIM анализ D триггера ( D{sh} ) прошел удачно, cmd файла нет, но свою логическую функцию триггер выполняет.

А вот со счетчиком проблема ( counter{sh} ) IRSIM вообще отказывается воспренимать, а ALS даграммы выдает,

но порядок счета и послдовательность состояний мне установить не удалось. Счетчик собиралась по предложенной

Ч. схемой. Хотелось бы услышать мнение остальных по поводу счетчика. А то собирать топологию по

непроверенной схеме как-то черевато.

Топология придложенной для тестового запуска микросхемы готова.

После небольшой дороботки опубликую библиотеку в группею. Необходимо узнать топологию падов.

Есть несколько наблюдений возьникших в ходе тестирования схемы.

IRSIM и ALS симмуляторы сильно подвели, с последовательной логикой не справился ни один.

Установить порядок счета и состояний счетчика и корректность работы дешефратора удолось только по результатам tran

анализа в spice3. По всей видемости, это наиболее достоверный способ тестирования схем. Хотелось бы конечно

добится адекватности и от внутренних симмуляторов. Что ты посоветуеш по этому поводу? Может быть отправить Стиву (Ruben) письмо

с приложенной библиотекой или задать аналогиный вопрос Диме Надежену.

На данный момент имеется библиотека с готоавым проектом (топологические и электрические ячейки) а так же .raw(spice3) файлы

с результатами поведеньческой симмуляции. Очень бы хотелось узнать о положении дел в П.П., успеваем ли мы передать топологию.

Так же бы хотелось перевести тополгическую картинку в требуемый формат для предприятия, может быть мы совсем нето и нарисовали.

P.S. очень сильно намучился с Electric, я конечно за него горой, но собрать в нем какой то проект (счетчик с дешефраторо я не считаю сложной схемой)

пердстовляется для меня ох как непростой задачей. На данный момент единственное, что радует это то что это opensource, ну и топологию с обеспечением связенности конечно удобно собирать. Может я чего то не допонемаю, но порой просто необяснимые веще пороисходили, при личной

встречи расскажу. Дешефратор собранный Т., на прверку оказался неработоспособным, пришлось пересобирать.

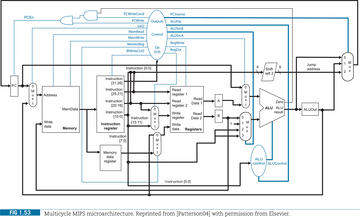

P.P.S. На мой взгляд Electric сыроват для серьезных рпазроботок, хотя мипс процессор то в нем собрали, да и Sun что то в нём делает, внес ясность в эти вопросы, а то как-то нехорошо, налево и напрво рассказываем какой он хороший, а на проверку то все совсем не так выходит.

Обещанная библиотека с результатами поведенческой симуляции.

Отредактировано ignat99 (2023-09-19 07:26:12)